AMALGHMA

This page describes some tools developed by our team MODCS – Modelling of Distributed and Concurrent Systems – in the context of hard real-time systems with energy constraints. More specifically, these tools have been developed for supporting the activities related to the software synthesis methodology described in the next section.

Methodology

Figure 1 depicts an overview of the proposed design methodology for implementing embedded software synthesis. This work assumes the tasks’ code was defined beforehand in order to provide a behavioral description in the system specification.

Initially, the designer defines the system specification, which consists of a set of concurrent tasks with their respective constraints, behavioral descriptions, information related to the hardware platform (e.g. voltage/frequency levels and energy consumption) as well as the system energy constraint. A measurement activity may be required whether the designer does not possess the tasks’ timing information or the information regarding the hardware energy consumption. Next, the specification is translated into an internal model able to represent concurrent activities, timing information, inter-task relations, such as precedence and mutual exclusion, as well as energy constraints. The adopted internal model is a time Petri net extension, labeled with energy consumption values. After generating the internal model (TPN), the designer may firstly choose to perform property analysis/verification or carry out the scheduling activity. This work adopts a pre-runtime scheduling method in order to find out a feasible schedule that satisfies timing, inter-task and energy constraints. Next, the feasible schedule is adopted as input to the automatic code generation mechanism, such that a tailored code is obtained with the respective runtime control, namely, dispatcher. Finally, the application is validated on a DVS platform in order to check system behaviour as well as the respective constraints. Once the system is validated, it can be deployed to the real environment.

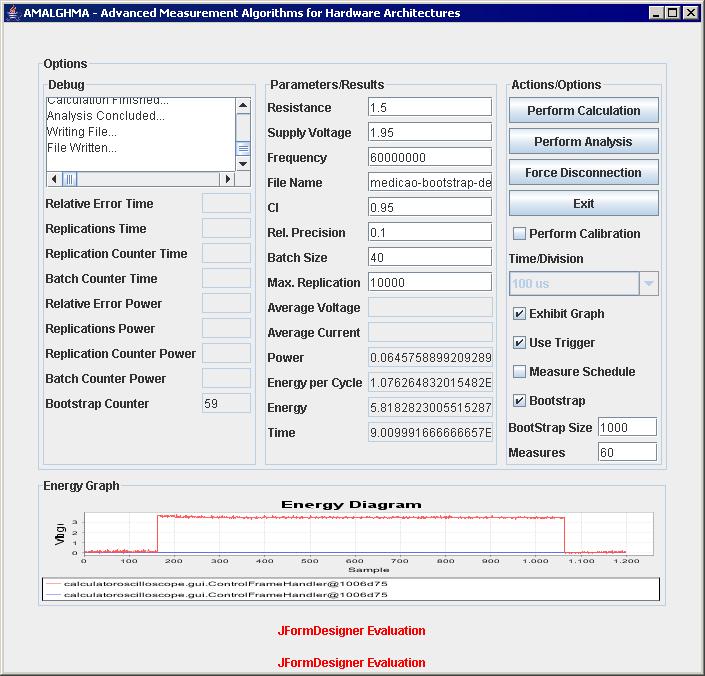

AMALGHMA Tool

AMALGHMA tool (Figure 2) – Advanced Measurement Algorithms for Hardware Architectures – has been adopted for automating the measuring activities. Firstly, the hardware characterization is performed, in such a way that the mean value of the energy consumption per clock cycle is obtained for each CPU voltage/frequency level. In this work, these values have been obtained by implementing a C function using the set of instructions common in the software application as well as the number of times that each instruction occurs. The measurement scheme is presented in Figure 3. In order to estimate power consumption, a PC running AMALGHMA is connected to an Agilent DSO03202A oscilloscope, which captures the CPU current draw by measuring the voltage drop across a 1 Ohm sense resistor. In this paper, the target platform is based on [1], which adopts a Philips LPC2106 processor, an 32-bit microcontroller with ARM7 core. Next, the worst-case execution cycles (WCEC) of each task and dispatcher (runtime support) are acquired. In this case, the oscilloscope is connected to an I/O port of the target CPU, which indicates tasks’ start and end times. It is important to state that the code of each task has been adjusted to force the respective worst-case execution cycles during the measurement process. Additionally, AMALGHMA adopts a set of statistical methods, such as bootstrap[2] and parametric methods[3], which are important in the measurement process due to several factors, for instance: (i) oscilloscope resolution; and (ii) resistor error. Besides, AMALGHMA has been validated considering LPC2106 datasheet as well as ARM7TDMI reference manual . For instance, considering the power consumption of LPC2106 core, the datasheet informs 0.054W, whereas AMALGHMA measured 0.059W, a difference of 5mW. Besides, a task was implemented considering 10000 clock cycles. AMALGHMA measured 10050 cycles during task execution, a difference of 50 cycles.

Bibliography

[1] Phatrapornnant, T., Pont, M., 2006. Reducing Jitter in Embedded Systems Employing a Time-Triggered Software Architecture and Dynamic Voltage Scaling. IEEE Trans. on Comp., 55(2):113–24.

[2] B. Efron, R. Tibshirani, An Introduction to the Bootstrap, Chapman and Hall, 1993

[3] Chung, C., Simulation Modeling Handbook – A Practical Approach CRC PRESS, 2004.